Lectures supported by practical demonstrations and a final design case. Course notes.

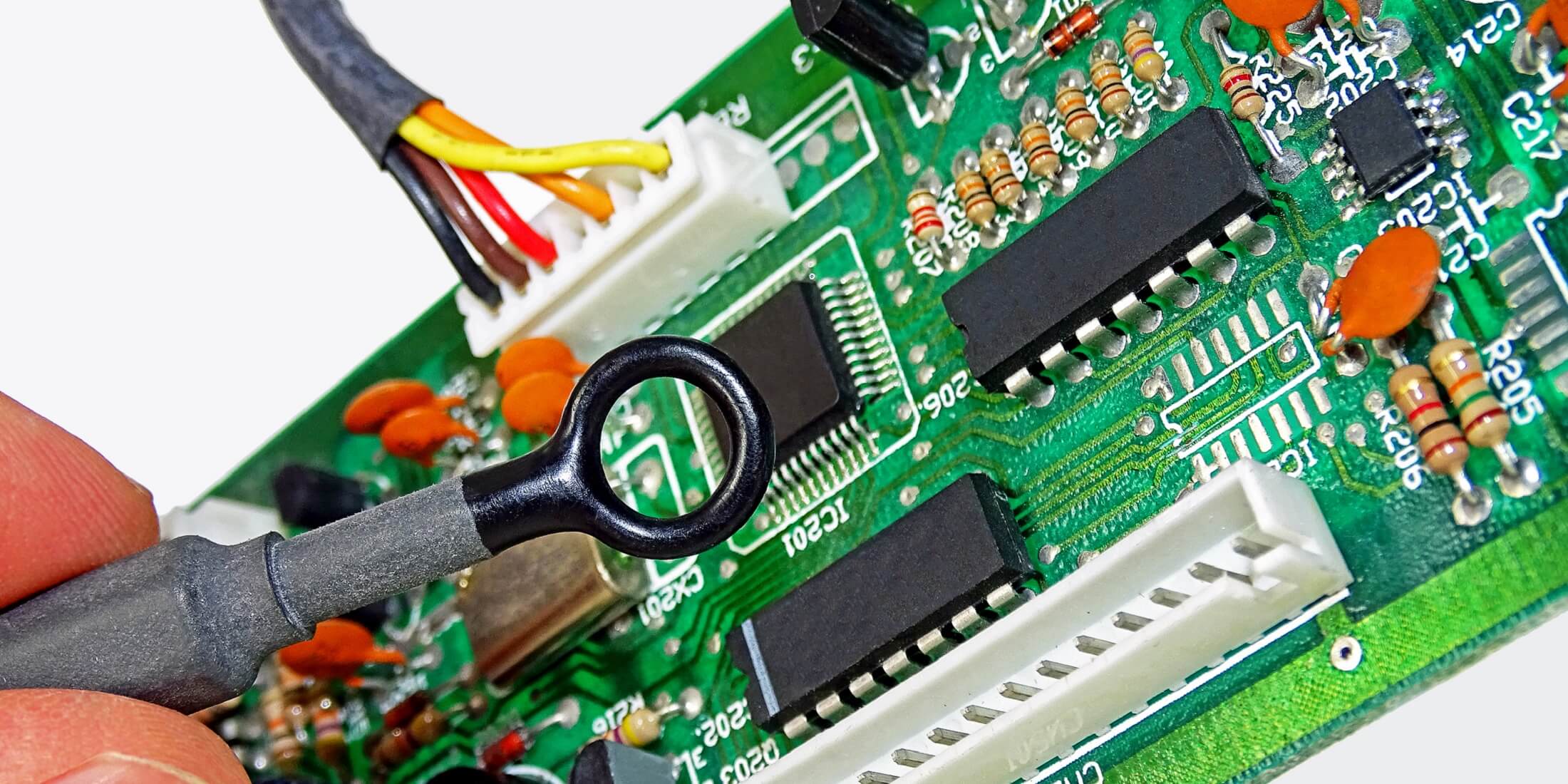

Electronic systems show increasing speed, power dissipation and density. The design, manufacture and simulation of a Power Distribution Network (PDN) for such systems become an increasing design challenge. A large number of supply voltages and signaling levels is used, timing and noise margins are reduced. The allowed noise on signals and power supply rails decreases while at the same time the density and bandwidth of interconnections increase. This means that the design of a power distribution network (power integrity) is not independent anymore from the signal integrity and electro magnetic compatibility (EMC) design domains. Power distribution design therefore becomes an important condition for good signal integrity and electromagnetic compatibility. The power distribution of a board is discussed from the perspective of power integrity with minimal mathematics and practical examples.

This training is available for open enrollment as well as for in-company sessions. For in-company sessions, the training can be adapted to your situation and special needs.

Objective

After the course, the participant will have basic knowledge of power integrity on board level and will be able to:

- determine the design requirements of a power distribution network;

- design a decoupling network impedance profile;

- select type, value and amount of decoupling capacitors to optimize performance and minimize cost;

- determine the effect of board layout and stack up on power distribution and how to optimize it;

- determine where to place decoupling capacitors;

- perform an analysis of a power distribution network;

- select tools to perform PDN simulations.

Target audience

This course is intended for electronic designers, board and IC designers, system architects. Educational level: At least BSc in electronics or physics. Prior knowledge on EMC is not required. The focus of the course is on board design and on the interface between the board and its IC’s. IC designers need to know how to interface an IC to a board and on its effect on the power distribution on the board and within the IC.

Program

Introduction

- Functions of a Power Distribution Network (PDN)

- Power delivery issues: Voltage fluctuations, timing errors

- Sources of power supply noise: Core and IO circuits

- Power distribution noise: Time and frequency domain

Power Distribution Network (PDN) Components

- DC-DC converter: Types, properties and model for PI analysis

- Bypass Capacitors: Characteristics, parasitics and models of various capacitor types

- Planes and traces: Low frequency model, high frequency response, resonances

PDN design procedure

- Target impedance, transient currents, chip and package effects, design from chip to DC-DC converter

Layout considerations

- Mounted inductance of capacitors, effect of traces, vias, planes

- Stackup selection, power plane location and separation

PDN impedance design

- Various methods, high frequency effects of capacitor location and plane size, determine value and amount of decoupling capacitors needed

- Interaction of power integrity, signal integrity and EMC

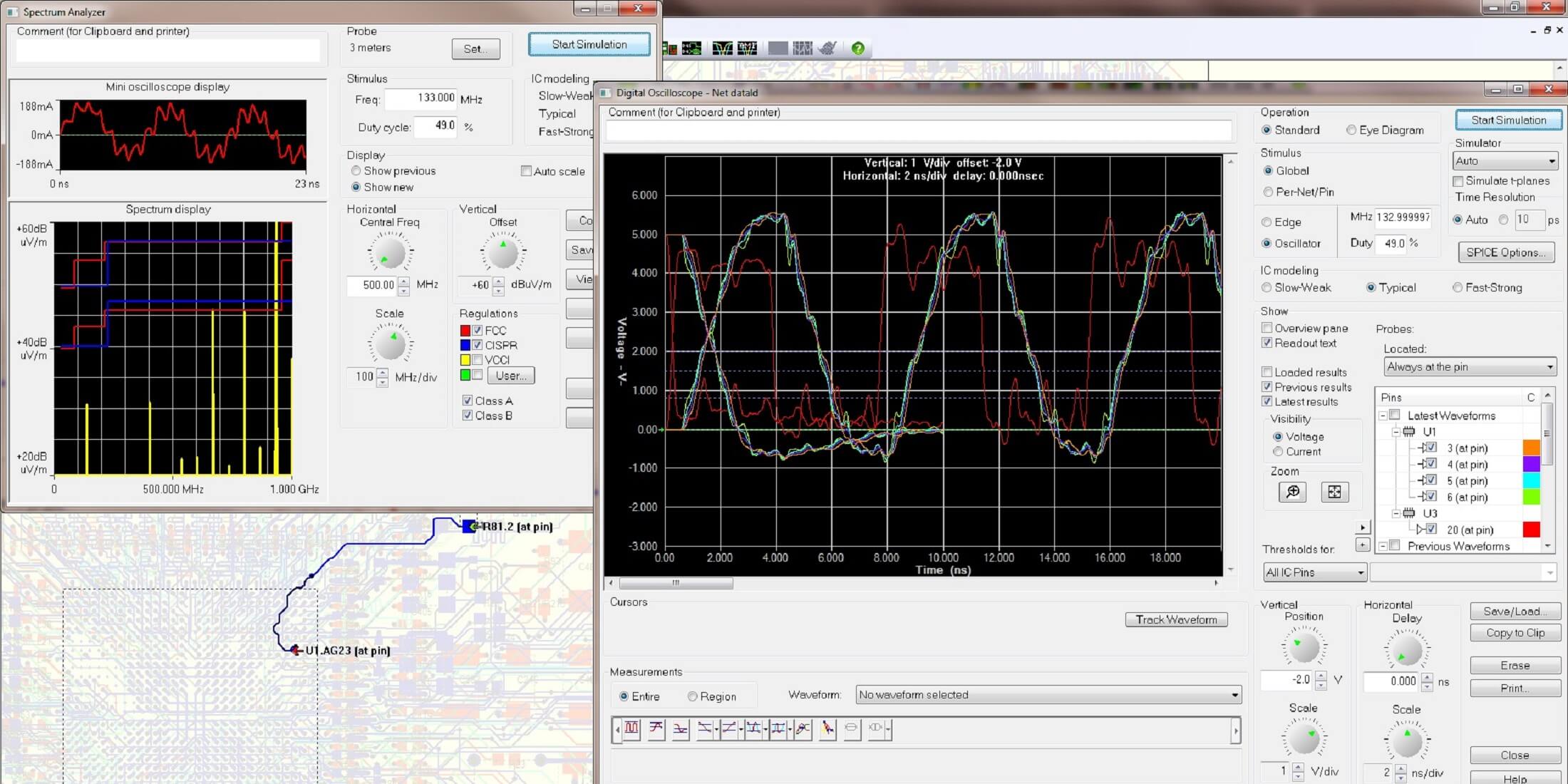

Simulation of a PDN

- Spreadsheets and SPICE simulation

- Advanced PI simulation: Pre- and post layout tool

PDN design example (exercise)

- Apply course knowledge in an exercise to design a PDN from beginning to end

Methods

Certification

Participants will receive a High Tech Institute course certificate for attending this training.

Remarks from participants